# 低消費電力システム設計に貢献する デジタルアイソレーター技術

**Digital Isolator Contributing to Low-Power System Design**

小林 和也 KOBAYASHI Kazuya 赤木 裕一郎 AKAGI Yuichiro 松田 克己 MATSUDA Masaki

デジタルアイソレーターは、電気的絶縁が必要な機器の通信・制御で安定動作を支える重要な役割を担っている。その 消費電力はシステム全体のエネルギー効率に影響を与えるため、カーボンニュートラルの実現に向け、産業や車載機器など 広範なシステムで、低消費電力化は重要な課題とされている。

東芝デバイス&ストレージ(株)は、民生用から産業・車載用まで、デジタルアイソレーターの低消費電力化を進めている。今回、新規回路を採用し、小型低消費電力4チャネルロジックを開発した。伝送データレートが1 Mビット/sで0.165 mA、25 Mビット/sで2.6 mAと、低消費電力であることを確認した。

The use of digital isolators, which are essential for the stable operation of various devices with communication and control functions while maintaining electrical insulation between high-voltage components, is expanding in various industrial and in-vehicle electronic systems. In recent years, demand for reducing digital isolator power consumption has increased, an area which is closely related to the total energy efficiency of such systems, as part of the movement to achieve carbon neutrality.

Toshiba Electronic Devices & Storage Corporation develops low power consumption digital isolators for a broad array of applications from consumer products to industrial and in-vehicle electronic systems. We developed a new compact, low power consumption quad-channel digital isolator by applying a new circuit, confirming its low power consumption with a data transfer rate of 0.165 mA at 1 Mbit/s and 2.6 mA at 25 Mbit/s.

## 1. まえがき

世界規模でのカーボンニュートラルへの動きの中, 我が国でも, 2050年カーボンニュートラル実現の目標に向けて, 特に温室効果ガスの排出割合が高いとされる電力・産業・運輸分野を中心に, 省エネルギー化や, 再生可能エネルギー化, デジタル化で, 高効率や脱炭素に結びつける取り組み・動きが加速されている<sup>(1)</sup>。国内の最終エネルギー消費全体の4割ほどを占めている製造業で消費されるエネルギーの高効率化は, 重要課題の一つとされている<sup>(2)</sup>。

製造現場の自動化に貢献するFA (ファクトリーオートメーション)機器や、HEV (ハイブリッド自動車)・EV (電気自動車)のインバーターやバッテリー制御などの高電圧を扱うシステムでは、安全性・信頼性・品質特性を確保するため、デジタルアイソレーターをはじめとするアイソレーションデバイスによるガルバニック絶縁 (電気的絶縁)が欠かせないものとなっている。

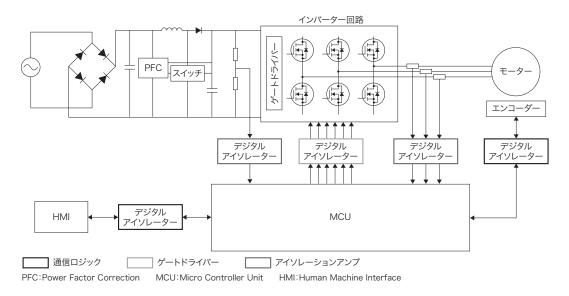

図1に示すように、デジタルアイソレーターは、MCU (モーターコントローラーユニット) などで構成される低電圧側の制御回路と、モーターや電源などの高電圧側の電源駆動回路との異電位間、あるいは同電位間など、グランドレベルの異なるシステム間で電気的絶縁を確保し、グランド

ループによるノイズの伝播を防止して、かつ、制御信号や 計測情報の確実な伝送を実現する。

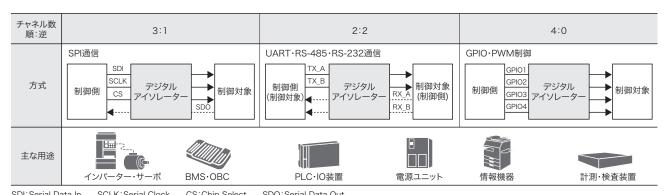

また、図2に示すように、インバーターやサーボのシステムにおける同期型シリアル通信方式のSPI (Serial Peripheral Interface)通信では、データを送受信するための信号線、データ送信のタイミングを指示する信号線、及びデータ送信先の選択を行う信号線の絶縁伝送に、1チャネルずつデジタルアイソレーターが使用される。非同期型シリアル通信方式のUART (Universal Asynchronous Receiver/Transmitter)や、汎用デジタル信号の送受信を担うGPIO (General Purpose Input/Output)制御と、電源やドライバー制御向けPWM (Pulse Width Modulation)制御伝送などでも、信号線の方向に合わせたシステムレベルの回路設計で、部品レイアウトに適したチャネル構成の絶縁伝送に、デジタルアイソレーターは頻繁に用いられる。

半導体デバイスが低消費電力化されると,基板内部の部品点数や配線長の最適化による機器の小型化が可能となり,システム全体として待機時や動作時の消費電力が削減される。

これにより、大規模データセンターや長期間連続稼働する産業機器のエネルギーコストの改善、フィールド端末など分散型制御システムのパフォーマンス向上、放熱対策の適

#### 図1. モーター駆動システムの機能ブロック図

通信ロジックは、コントローラーと周辺ブロック間の信号通信に対応し、ゲートドライバーは、パワーデバイスのゲート制御に対応する。アイソレーションアンプは、バス電圧やセンシング電流を監視してコントローラーへ伝える。

Example of application of digital isolators to motor drive system

SDI:Serial Data In SCLK:Serial Clock CS:Chip Select SDO:Serial Data Out RS-485, RS-232:EIA (Electronic Industries Association:米国電子工業会)のシリアル通信規格 TX:Transmitter RX:Receiver BMS:パッテリーマネジメントシステム OBC:オンボードチャージャー PLC:プログラマブルロジックコントローラー IO:入出力

## 図2. 4チャネルロジックの場合のデジタルアイソレーターの用途例

4チャネルロジックデジタルアイソレーターは、多様な用途において、信号通信・制御伝送に対応する。

Quad-channel digital isolators used in various applications

正化による高密度実装化の進展など、幅広い分野での省エネルギー化に寄与することが期待される。

ここでは、デジタルアイソレーターで、安定したデータ伝送を維持しながら、低消費電力化との両立を実現した技術について述べる。

## 2. デジタルアイソレーターの基本構造と絶縁性能

東芝デバイス&ストレージ(株)は、2023年にデジタルアイソレーター参入製品としてDCL541x01(xは、L又はHを意味する記号)などロジック4チャネル製品を開発し<sup>(3)</sup>、リ

リースした。これは、高速動作、高絶縁性能、高耐ノイズ性を重点としていた。

今回, 多彩な市場ニーズに対応するため, 低消費電力に フォーカスした小型のデジタルアイソレーターを開発した。

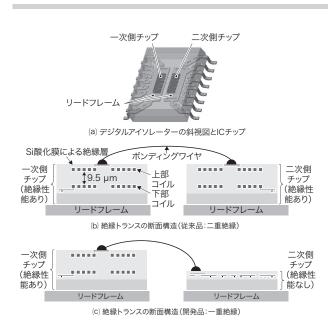

#### 2.1 基本構造

基本構造を図3に示す。CMOS (相補型金属酸化膜半導体)プロセスに絶縁トランスを集積化した一次側と二次側の二つのICチップを、1パッケージ内に実装している(図3(a))。絶縁トランスの上部・下部コイルの層間膜には、Si(シリコン)酸化膜を用いた。Si酸化膜は、1μm当たり約

#### 図3. デジタルアイソレーターの構造

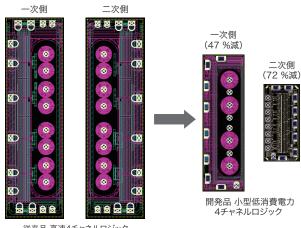

パッケージ内に、一次側と二次側のICチップを実装する。従来品は、一次側・二次側チップとも上部・下部コイル間を $9.5\,\mu m$ の厚い絶縁層で電気的に絶縁した絶縁トランスを形成し、信号は磁気結合で伝送する。開発品は、一次側チップだけに絶縁トランスを形成する。

New digital isolator device structures

$500\,V_{rms}$  (実効値)の優れた絶縁耐圧を持ち、かつ湿度や温度に対しても安定な材料である。CMOSプロセスで用いる高品質なSi酸化膜を $9.5\,\mu m$ と厚く形成し、絶縁性能を確保した。

従来品のDCL541x01は、二つの絶縁トランスをカスケード接続した二重絶縁構造としていた(図3(b))。今回開発した小型低消費電力デジタルアイソレーターでは、機能絶縁用途に特化し、トランスの結合効率を向上させるため、絶縁トランスを一次側チップだけに形成した。これを便宜的に一重絶縁と呼ぶ(図3(c))。

#### 2.2 動作電圧における絶縁寿命

デジタルアイソレーターの絶縁性能は、製品の寿命期間中の連続動作において印加される電圧下で損なわれてはならない。開発品の小型低消費電力デジタルアイソレーターでは、チップ上の絶縁構造を従来品DCL541x01の二重絶縁から一重絶縁とし、連続動作電圧もスケーリングさせて1/2相当とすることで、従来品と同等に、故障率1ppmで絶縁寿命37.5年以上が得られた。

## 3. 回路構成

小型パッケージSSOP16に収まるチップサイズと、低消費電力が市場からの主要求であり、極力シンプルで小規模な回路構成をコンセプトに設計した。低消費電力化として

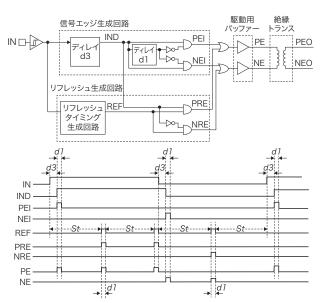

St: REFの定期的なパルス間の時間

REF:リフレッシュタイミングパルス NRE:マイナスリフレッシュエッジ NE:絶縁トランス一次側マイナスエッジ NEO:絶縁トランス二次側マイナスエッジ た各時間

## 図4. 絶縁トランス一次側送信部回路図と動作タイミング

採用したエッジ伝送方式で、データリフレッシュに必要なリフレッシュパルス の発生と伝送に重畳させるため、概念を示す。

Transmitter circuit on primary side of transformer and operation timing chart

は、入力信号のエッジ検出と切り替え時にだけ1 ns以下の 1ショットパルスを送受信することを組み合わせた信号の伝 送方式(以下、エッジ伝送方式と呼ぶ)を採用した<sup>(4)</sup>。

## 3.1 絶縁トランス一次側(送信部)

絶縁トランス一次側の送信部は、高周波搬送波が不要で、標準値0.8 ns幅の1ショットパルスのPEI(入力立ち上がりエッジ)、NEI(入力立ち下がりエッジ)をエンコードし、駆動用バッファー回路はシンプルなインバーター多段構成で設計した。図4に送信部回路図と動作タイミングを示す。

また、信号切り替え時にしか信号伝送させないエッジ伝送方式を採用したことにより、受信側の電源起動時に送信側入力の極性が判断できないため、定期的にリフレッシュパルスを伝送するリフレッシュ生成回路を装備している。リフレッシュパルスは、入力ハイ期間に立ち上がりエッジを発生させたパルスと同じ出力端子から発生させ、入力ロー期間に立ち下がりエッジと同じ出力端子から発生させるものであり、取りこぼしたエッジ信号を本来あるべきデータ極性に戻すことが可能である。

## 3.2 絶縁トランス二次側(受信部)

絶縁トランス二次側の受信部は、データエッジ信号検波 回路とリフレッシュ検波回路、スイッチ回路1,2で構成した。

## 図5に受信部の回路図と動作タイミングを示す。

データエッジ信号検波は、絶縁トランス一次側から送信したパルスの二次側コイルのPEO (絶縁トランス二次側プラスエッジ)又はNEO (絶縁トランス二次側マイナスエッジ)をGND (接地)にすることでインバーター検波を可能にした。リフレッシュ検波は、リフレッシュ信号を受信するタイミングでデータ補正の要らない正常動作中、エッジ信号待ち受け部と逆相がPGS (プラスシャントゲート)又はNGS (マイナスシャントゲート)によりGNDシャントされているため、負電圧パルスとなってPEO、NEOに信号が現れる。これを受信するための負電位パルスの受信回路を装備している点が、特徴の一つである。また、正負の極性を持つ信号を同一信号線で受信するアーキテクチャー上、データエッジと誤検波しないためのコイル不要輻射(ふくしゃ)を抑える必要があり、

駆動用 絶縁トランス バッファ -タエッジ信号検波回路 PE PEO PEG OUT -NED NEG NE NFO スイッチ回路2 RGS F1V1 d4 リフレッシュ検波回路 負電位 NRD 検波 RD ウオッチ ドッグ 負電位 PRD 検波 遅延回路 スイッチ回路1 ディレイ PGS d2 IND PE NE PEO <u></u> OUT PRD NRD PGS **d**2 NGS d4 ★ d4 ⊓ RGS PEO, NEOの不要輻射をRGSで除去 PEG:立ち上がりエッジゲート NEG:立ち下がりエッジゲート PED:立ち上がりエッジ検出 NED:立ち下がりエッジ検出 OUT:出力 NRD:マイナスリフレッシュ検出 PRD:プラスリフレッシュ検出 RD:リフレッシュ検出 SIGDET: Signal Detection (信号検出) RGS d2, d4: ディレイd2, ディレイd4で設定した各時間 RGS: リフレッシュシャントゲート

#### 図5. 絶縁トランス二次側受信部の回路図と動作タイミング

データ受信とリフレッシュパルス受信を確実に実施するため、回路のブロック図と動作タイミングチャートで示すスイッチ制御が必要である。

Receiver circuit on secondary side of transformer and operation timing chart

リフレッシュ信号検波後に不要輻射を除去するスイッチ回路 2を装備した。

従来品 高速4チャネルロジック (DCL541L/H01)

#### 図6. チップ小型化イメージ

小型化に特化した回路設計を行い、従来品DCL541x01と比較して、一次側47%、二次側72%を削減した小型化を実現した。

Conventional and new digital isolator chip size comparison

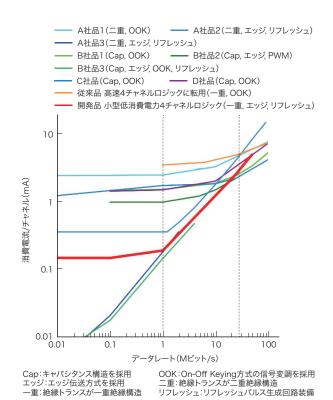

## 図7. 消費電流のデータレートトレンドの市販品との比較

開発品は、 $1 \sim 4 \, \text{M E in } / \text{Som}$  作領域ではA社品3・B社品3とほぼ同等、 $4 \sim 25 \, \text{M E in } / \text{N E in } / \text{M E in } / \text{$

$Competitor\ digital\ isolators\ and\ new\ digital\ isolator\ current\ consumption\ comparison$

レイアウト寄生抽出後の検証を行い、フィードバック遅延、素子サイズを最適化し、誤動作なしを実現している。

#### 3.3 小型化の実現

4チャネル分のトランスコイル形状は、8の字コイルではなく円形を採用し、一重絶縁として、二次側チップはコイルなしである。回路形式も小型化に特化し、図6に示すチップの小型化を実現した。従来品DCL541x01と比較して、高速ロジック面積は、一次側チップで47%、二次側チップで72%を削減できた。

## 3.4 消費電流

消費電流は、電源電圧、動作可能周波数,及び回路形式で、大きく異なる。**図7**に、電源電圧 $V_{dd}$ が3.3 V,容量負荷 $C_L$ が15 pFの標準値条件で、1 チャネル当たりの消費電流を、市販品8種類と比較して示す。開発品のICは伝送データレート1 Mビット/sから最大25 Mビット/sをターゲットとしており、A社品2が近い伝送方式である。 $1\sim25$  Mビット/sの動作領域では、比較した全ての市販品とほぼ同等かそれよりも低い消費電流であり、これらの市販品とほぼ同等かそれ以上の低消費電力化を実現したことを確認した。

## 4. あとがき

絶縁信号伝送部にエッジ伝送方式の新規回路技術を採用したことで、低消費電力を実現した小型デジタルアイソレーターについて述べた。

今後も、省エネルギー社会の実現に貢献するデジタルアイソレーターのラインアップ展開や性能向上に向けた開発を進めていく。

# 文 献

- 内閣官房、ほか、2050年カーボンニュートラルに伴うグリーン成長戦略、 2021、91p、<a href="https://www.meti.go.jp/policy/energy\_environment/global\_warming/ggs/pdf/green\_gaiyou.pdf">https://www.meti.go.jp/policy/energy\_environment/global\_warming/ggs/pdf/green\_gaiyou.pdf</a>, (参照 2025-07-07).

- (2) 資源エネルギー庁, ほか. 省エネルギー・非化石エネルギー転換技術 戦略2024. 2024, 17p. <a href="https://www.meti.go.jp/press/2024/05/20240514004/20240514004-1.pdf">https://www.meti.go.jp/press/2024/05/20240514004/20240514004-1.pdf</a>, (参照 2025-07-07).

- (3) 卵尾豊明, ほか. カーボンニュートラル実現に貢献する高ノイズ耐性 のデジタルアイソレーター. 東芝レビュー. 2023, **78**, 1, p.32–36. <a href="https://www.global.toshiba/content/dam/toshiba/jp/technology/corporate/review/2023/01/a09.pdf">https://www.global.toshiba/content/dam/toshiba/jp/technology/corporate/review/2023/01/a09.pdf</a>, (参照 2025-07-07).

- (4) Toshiba, Toshiba Electronic Devices and Storage. Nagata, M. Digital Isolator. U. S. Patent 12155508B2. 2024-11-26.

小林 和也 KOBAYASHI Kazuya 東芝デバイス&ストレージ(株) 半導体事業部 IC開発センター Toshiba Electronic Devices & Storage Corp.

赤木 裕一郎 AKAGI Yuichiro 東芝デバイス&ストレージ(株) 半導体事業部 半導体応用技術センター Toshiba Electronic Devices & Storage Corp.

松田 克己 MATSUDA Masaki 東芝デバイス&ストレージ(株) 半導体事業部 アナログIC製品技術部 Toshiba Electronic Devices & Storage Corp.