# システム基板の耐ノイズ設計を高効率化する 半導体 EMC 検証モデル

EMC Simulation Model to Efficiently Verify Noise Tolerance of Automotive Semiconductor Devices Mounted on System Circuit Boards

冨島 敦史 TOMISHIMA Atsushi 一 今泉 祐介 IMAIZUMI Yusuke - 宮原 秀敏 MIYAHARA Hidetoshi

自動運転・コネクテッドに対応する電子プラットフォームが急速に進化する中で、車両や車載ECU(電子制御ユニット)の ノイズ耐性確保が最重要の課題となっている。その実現のために、半導体単体に対しても厳しいノイズ耐性が求められ、イ ミュニティーや静電気放電(ESD)耐性といったノイズ耐性を予測するシミュレーション技術の要求も高まっている。

東芝デバイス&ストレージ(株)では、半導体のイミュニティー及びESD耐性に対するシミュレーション環境を構築し、シミュレーション用モデルの開発・検証を行った。このモデルを用い、実際に半導体をシステム基板に実装してノイズ耐性を予測した結果、解析値と実測値がよく一致することを確認した。

With the rapid progress of electronic platforms for autonomous driving and connected vehicles, ensuring higher electromagnetic noise tolerance for in-vehicle electronics and electronic control units (ECUs) is an issue of vital importance. Semiconductor devices in automotive applications are also required to meet exacting specifications related to electromagnetic noise including conducted immunity and electrostatic discharge (ESD) immunity, leading to growing demand for simulation techniques to predict immunities for individual devices.

Toshiba Electronic Devices & Storage Corporation has constructed a simulation environment that can evaluate both conducted and ESD immunities of semiconductor devices mounted on various system circuit boards, confirming that the analytical values and measured values match well in actual cases.

# 1. まえがき

昨今の半導体開発では、低電圧化・大電流化、信号の高速化、半導体チップやパッケージの小型化などが要求されており、これらは全て、半導体のノイズ耐性確保に対する条件が厳しくなる方向である。CASE (Connected, Automated, Shared & Services, Electric)と呼ばれる自動車業界が注力する各領域での先端技術の要求に対して、製品の誤動作などによる不具合発生を避けるため、イミュニティーと呼ばれるノイズ耐性の確保が重要な課題となっている。

また、ロバストなシステム開発が求められる中で、EMC (電磁両立性)特性を製品製造前に把握し、システム基板全体のEMC性能を事前に解析で予測する、いわゆるフロントローディングへの要望は高い。

製品開発時に、実設計したシステム基板データを電磁界解析ツールに取り込み、モデルを抽出することで、実レイアウト相当の結果の推測ができる。しかし、最適化を目的に、基板レイアウトや部品数などが変わる場合は、設計変更後の基板製造と評価を待つ必要がある。一方、想定される変更点の特性を回路解析モデルに組み込めば、影響を加味し、より早い段階でのシステム基板設計変更要否の判断をすることができ、製品開発サイクルの短縮が可能となる。

ここでは、半導体に対するEMC試験規格及びEMCモデリング規格の全体像を説明した後、伝導イミュニティーとESD耐性についてのシミュレーションの実施例、及びモデルの課題について述べる。

# 2. 半導体集積回路のEMCに関する国際規格

半導体集積回路のEMCに対する国際規格を,表1に示す。これらは半導体単体を対象に、半導体自身のEMC特性を把握することを目的としているが、測定結果のシステム設計への活用が検討されている。

# 表1. 半導体集積回路のEMCに関する国際規格

List of international standards related to electromagnetic compatibility (EMC) requirements for integrated circuits

| 分 類                | 規格名                        | 内 容              |

|--------------------|----------------------------|------------------|

| エミッション測定 (EMI)     | IEC 61967シリーズ              | 伝導・放射測定法         |

| イミュニティー測定<br>(EMS) | IEC 62132シリーズ              | 伝導・放射測定法         |

| インパルスイミュニティー<br>測定 | IEC 62215シリーズ              | 伝導パルス測定法         |

| ESD                | IEC 61000-4-2<br>ISO 10605 | 接触・気中放電          |

| バストランシーバー評価        | IEC 62228シリーズ              | 伝導EMI・EMS測定, ESD |

| EMC ICモデリング        | IEC 62433シリーズ              | EMCシミュレーションモデル   |

EMI: 電磁干涉 EMS: 電磁感受性

EMCの事象に合わせて、エミッションについては国際電気標準会議(IEC)のIEC 61967シリーズに、イミュニティーについてはIEC 62132シリーズに、それぞれ伝導・放射に対する半導体独自の複数の測定方法が、アプリケーションや目的に応じて規格化されている。インパルスイミュニティー測定についてのIEC 62215シリーズと国際標準化機構(ISO)のISO 7637シリーズ、及びESDについてのIEC 61000-4-2とISO 10605では、システムレベル試験と同等の条件での試験が適用される。

また、バストランシーバー評価についてのIEC 62228シ リーズでは、トランシーバーICを同一基板上に複数実装 し、通信を行った状態でEMC評価を行うなど、実システム に近い状態での評価法が規格化されている。

これらに加えて、半導体のシミュレーション用モデル規格であるIEC 62433シリーズでは、モデルの構成要素やフォーマットなどが定義されている。この規格では、モデルの作成方法までは定義されておらず、ユーザーに委ねられている。

# 3. モデリング・シミュレーション実施例

システム基板全体でのEMC解析を実施するには、基板・受動部品・半導体それぞれのモデルを作成し、目的に応じて、モデル化及び解析手法を適切に選択する必要がある。以下に、伝導イミュニティー及びESD解析を目的とした実施例を示す。

# 3.1 伝導イミュニティーシミュレーション

伝導イミュニティーモデルについてのIEC 62433-4<sup>(1)</sup>は, ICピンに印加された伝導ノイズに対するイミュニティーレベルの予測に使用することを目的とする。

## 3.1.1 モデル作成

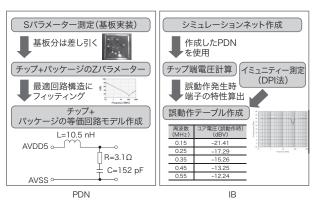

IEC 62433-4では、モデル構成要素として、受動回路網 (PDN: Passive Distribution Network) と誤動作テーブル (IB: Internal Behavior) が定義されており、これに従って実半導体の実測結果からそれぞれの要素を作成した。 図1に、手順を示す。

PDNは、半導体を実装した基板のSパラメーターを測定し、解析で求めた基板単体のSパラメーターを差し引いた(De-embedded)後にフィッティングすることで、半導体チップとパッケージだけの等価回路モデルを求めた。IBは、PDNを用いてICチップ端の電圧を求め、IEC 62132-4のDPI (Direct RF (Radio Frequency) Power Injection)法に基づいた伝導イミュニティーの測定結果から、誤動作発生時の電源電圧テーブルを作成した。

#### 3.1.2 シミュレーションの実行

IBモデルでは、誤動作発生時のIC電源パッド電圧が導

出されており、システム検証時にコンデンサーの有無などのシステム基板側の条件を変えたときの電圧と比較することで、DPI試験結果(誤動作発生の有無)を予測できる。

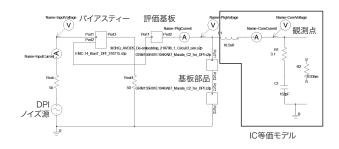

3.1.1 項で作成した半導体モデルを、システム基板と基板 部品モデルに組み込んだ**図2**の DPI 試験のシミュレーション 回路を作成し、システム基板や基板部品を変更して解析を 行うことで、最適化を検討する。

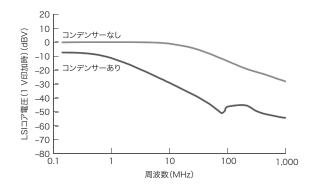

図2のDPI試験シミュレーション回路において、基板部品であるコンデンサーの有無についての解析を行い、ノイズ印加電圧を1VとしたときのICチップのアナログ電源パッドに発生するコア電圧を求める。図3のとおり、コンデンサーを実装することにより、コア電圧の変動が抑えられることが分かる。すなわち、ノイズ印加時に、ICへの影響が減少することを示している。

L:インダクタンス C:キャパシタンス R:抵抗 AVDD5, AVSS:アナログデジタルコンバーターのアナログ電源端子

# 図1. PDN及びIB作成手順

伝導イミュニティーモデル  $(ICIM-CI)^{(I)}$  の構成要素である PDN 及び IB の、 測定結果からの作成手順を示す。

Creation of passive distribution network (PDN) and internal behavior (IB) models

#### 図2. DPI試験のシミュレーション回路

基板設計最適化のために、チップのアナログ電源パッドに発生する電圧値 を解析するためのDPI試験回路図を示す。回路解析を用いることで高速に 結果を取得でき、最適化検討に適した手法である。

Simulation circuit model to evaluate conducted immunity by direct radio frequency power injection (DPI) method

図3. ICチップ上のアナログ電源パッドに発生するコア電圧のコンデンサー実装の有無による差異

コンデンサーを実装することにより、コア電圧の変動が抑えられ、ノイズ印加時のICへの影響が減少する。

Changes in input voltage at power pad of IC chip mounted on board with and without capacitance

この結果とIBモデルから、ノイズ耐量の指標であるDPIノイズ印加時の誤動作発生電力が計算できる。実際のシステム基板設計では、基板や半導体の小型化や、狭ピッチ化による空きスペースの不足など、様々な要因で部品配置に制約を受けるケースが多い。そこで、レイアウトの影響を考慮した検証も合わせて実施した。

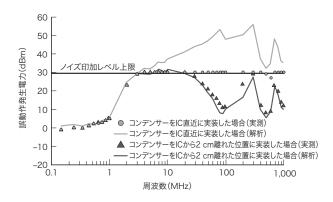

図4に、DPI評価基板上のIC直近にコンデンサーを実装した場合と、IC端子からコンデンサーが2cm離れているケースを想定し、2cmの配線分の寄生インダクタンス成分を基板部品部に追加した場合の解析値を、実測値(最大印加電力30dBm)と比較して示した。IC端子からコンデンサーが離れているケースの実測では、基板上にインダクター部品を実装し、コンデンサー位置までの配線分を模擬した。

IC直近にコンデンサーを実装した場合では、ノイズ印加レベル上限以下で誤動作が発生している3 MHz以下の帯域での実測値と解析値の差異が±3 dB以内であり、イミュニティーレベルの改善予測が可能なことを確認できた。ただし、500~600 MHzの帯域では、誤動作発生電力と周波数に若干のずれが見られており、この原因については、別途検討する必要がある。

一方、コンデンサーがIC直近に実装できない場合については、3 MHz以下の帯域ではIC直近にコンデンサーを実装した場合と同様の結果が得られているが、3 MHz以上の帯域ではIC-コンデンサー間の配線のインダクタンス成分により、コンデンサーの効果が低下し、IC直近に実装した場合と比較して、ノイズ耐量が低下する結果が得られた。実レイアウトを正確に再現した解析を実施しないと、実測と異なる結果が得られることもあり、十分注意する必要がある。こ

図4. 誤動作発生電力の実測値と解析値のコンデンサー実装位置による違い

コンデンサーをIC直近に実装した場合では、ノイズ印加レベル上限以下で 誤動作が発生している周波数帯域での実測値と解析値の差異が±3dBm以 内であり、イミュニティー耐量レベルの改善を予測できることが確認できた。

Differences between measured and simulated power-line noise thresholds triggering failure according to location of capacitance

のように、回路図上には現れない寄生成分などを考慮して 解析モデルを構築することにより、システム基板のレイアウト を含めて、最適化できる。

## 3.2 ESD耐性シミュレーション

次に、基板のESD耐性に対する検討事例を示す。製品の耐ノイズ性能評価として、静電気試験が広く行われているが、半導体に対しても、システム試験規格(IEC 61000-4-2, ISO 10605(車載向け))への準拠が要求されており、厳しいESD耐性が求められる。このため、基板上にESD対策部品を実装するなどの効果的な対策が必要になる。基板上にESDノイズが印加されたときのIC端への伝搬ノイズ量を予測し、ICの破壊しきい値を超えないように基板設計を最適化する。

## 3.2.1 モデル作成

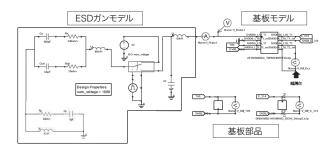

静電気解析では、印加用ESDガンの等価モデル、電磁 界解析による基板モデル、及び部品ベンダーが公開している基板部品モデルを用い、ICについては簡易等価コンデンサーモデルを付与し、これらを組み合わせた図5のシミュレーション回路モデルを作成した。

## 3.2.2 シミュレーションの実行

ESD ガンモデルからIEC 61000-4-2に準拠した印加波形が出力され、これを基板モデルに入力してIC端へのノイズ 伝搬量を計算する。イミュニティーシミュレーションと同様に、ESD対策部品であるTVS (Transient Voltage Suppression) ダイオードとコンデンサーの組み合わせを任意に変更し、これを基板モデルに入力してIC端での電圧波形を比較することで最適化を行う。

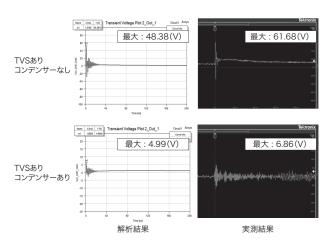

図6に、基板上コンデンサーの有無について比較した結

#### 図5. ESD試験のシミュレーション回路

ESD波形を印可した際にチップへ伝搬するノイズ量を解析で求める手法は、 迅速に結果が得られ、基板設計最適化の検討に適している。

Simulation circuit model to evaluate ESD

図6. ESD試験によるノイズ伝搬レベルの実測結果と解析結果の比較解析結果と実測波形の比較からノイズ伝搬レベルが解析により再現できていることが分かる。

Comparison of measured and simulated noise propagation caused by ESD

果の例を示す。ESD印加点とIC端の間にコンデンサーを付与することにより、ICへのノイズ伝搬レベルの低減が観測され、コンデンサーの効果が確認できる。また、実測でも同様のノイズ伝搬レベルの低減が確認されており、解析結果に基づく基板最適化の検討が実行可能であることを示した。

#### 3.3 シミュレーションまとめ

基板設計を最適化するには、基板レイアウトや部品を変更するなど複数の条件での解析が求められる。また電磁界と回路の解析手法を組み合わせ、解析時間を短縮することも必要となる。解析によって求められた結果を、システム製品開発に正しく適用していくために、今後も解析目的に応じたモデル、及びガイドラインの提供に向けて、検証を継続していく。

## 4. モデリングの課題

イミュニティーシミュレーションでは、対象とするICの複雑な機能の全動作モードを網羅したモデルを作成することは難しい。ここで示したモデル作成事例も、ある特定の動作条件での誤動作例に基づいて作成したことに、留意する必要がある。モデルの作成側と使用側で、これらの条件の整合を取ることで、精度の高いシミュレーションを実現できる。

また、新規のシステム設計時に解析を実施するために、IC設計途中段階で、設計データから作成が可能なモデルの検討も、今後必要とされる。

## 5. あとがき

IECで国際規格化された伝導イミュニティーモデル(IEC 62433-4準拠)と、静電気解析モデルを作成し、システム検証への適用事例から、モデルの有用性を確認した。

今後、3章に示した周波数領域による差異の原因や、4章に示したモデリング課題に対する解決策やモデル適用範囲などを検討し、半導体モデルのシステム検証への適用とガイドライン化を進めていく。

# 文 献

(1) IEC 62433-4: 2016. EMC IC modelling - Part 4: Models of integrated circuits for RF immunity behavioural simulation - Conducted immunity modelling (ICIM-CI).

**冨島 敦史** TOMISHIMA Atsushi 東芝デバイス&ストレージ (株) 半導体事業部 パッケージ&テスト技術開発センター Toshiba Electronic Devices & Storage Corp.

今泉 祐介 IMAIZUMI Yusuke 東芝デバイス&ストレージ(株) 半導体事業部 パッケージ&テスト技術開発センター Toshiba Electronic Devices & Storage Corp.

宮原 秀敏 MIYAHARA Hidetoshi 東芝デバイス&ストレージ(株) 半導体事業部 パッケージ&テスト技術開発センター Toshiba Electronic Devices & Storage Corp.