# イジングマシンによる量子ビットマッピング最適化

濱川 洋平 $^{1,a}$ ) 田村 亮太 $^1$  柏俣 智哉 $^1$  辰村 光介 $^1$  今井 浩 $^2$

概要:現在の量子コンピュータでは、量子ビットのノイズやエラーが計算精度に大きな影響を与えるだけでなく、量子ビット間の接続(トポロジー)による物理的制約も存在するため、これらを考慮した量子ビットマッピングが不可欠である。本研究では、デバイスのノイズ分布を考慮した量子ビットマッピング問題を二次制約無し二値最適化(Quadratic Unconstrained Binary Optimization, QUBO)に定式化し、QUBOやイジング問題の高速求解に特化した計算機であるイジングマシンを使って最適なマッピングを求める手法を提案する。手法の検証にあたり、種々のバリエーションを持つ仮想トポロジーや実際の IBM 量子コンピュータを対象とし、イジングマシンには FPGA(Field Programmable Gate Array)および GPU に実装したシミュレーテッド分岐(Simulated Bifurcation)を用いた。従来手法に対し、一部の条件においてマッピングの精度とマッピングを求める計算時間に優位性があることを実証した。

# 1. はじめに

近年、ゲート型量子コンピュータのための量子ハードウェア(デバイス)やアプリケーション開発のための量子回路コンパイラ(トランスパイラ)が急速に発展している.現在のデバイスには、実行可能な量子ゲート種類の制約、量子ビットの隣接結合制約(トポロジー制約)などの物理的な制約が存在する。また、ノイズや量子ゲート操作、量子ビット読み出し操作に伴うエラーも大きな課題である。量子回路コンパイラは、これらの物理的制約を解決しながら、エラーの影響を最小化することで高忠実度の回路生成を目指す[1,2]。この過程で、論理(仮想)量子ビットとデバイス上の物理量子ビットの対応関係(組合せ)を最適化する処理を量子ビットマッピングと呼ぶ。

現在のデバイスでは、量子ビットや量子ビット間結合ごとにエラー率が変動し、時間経過とともに推移する。そのため、デバイス実行の都度、これらを考慮した量子ビットマッピングが行われることが望ましい。ノイズを考慮した量子ビットマッピング手法 [3] は存在するが、多くの場合後に続くルーティング処理 (隣接結合制約解決のためのSWAPマッピング)による追加ゲートの影響が支配的になるため、最初に決めたマッピングが有効に機能するとは限らない。また、クラウドアクセスを前提とする現在の量子コンピュータシステムでは、コンパイルされた量子回路が実行されるまで、キュー待ちなどの時間経過に伴いエラー

分布が変動する可能性もある.

近年、組合せ最適化問題を高速に解くために特化した計 算機であるイジングマシン [4–29] が注目され,研究されて いる. 組合せ最適化問題とは, 有限個の選択肢の中から, 特定の制約条件の下で目的関数を最適化する組合せを見つ ける問題であり、代表的な例として巡回セールスマン問題 やスケジューリング問題が挙げられる. これらの問題は, 問題サイズに応じて解空間が指数的に大きくなることから 厳密な最適解を求めることが難しい. イジングマシンは, ±1 のいずれかをとるイジングスピンと呼ばれる変数の 2 次式で与えられたエネルギーを最小化する組合せ最適化問 題(イジング問題)を近似的に解く専用計算機である.多 くの組合せ最適化問題がイジング問題に定式化できる [30] ことが知られている. また, 主に0と1のいずれかをとる バイナリ変数による二次制約無し二値最適化 (Quadratic Unconstrained Binary Optimization, QUBO) もイジング 問題と等価であることから、QUBO もイジングマシンで解 くことができる.

本研究では、量子ビットマッピング問題を QUBO に定式化し、イジングマシンを使って最適なマッピングを求める手法を提案する. イジングマシンを用いた量子回路最適化手法はいくつか提案されているが [31-33]、本手法は、通常の量子回路コンパイラの後段に位置する独立したプロセスとして定義されることが特徴であり、予めルーティングまたは量子回路コンパイラによりデバイスのトポロジーに最適化済みの物理量子回路を入力とし、デバイスのノイズ分布を考慮した再マッピングを目的とする. 再ルーティングを伴わないことから演算負荷が小さく高速に動作する

<sup>1</sup> 株式会社東芝 研究開発センター

<sup>2</sup> 東京大学医科学研究所ヒトゲノム解析センター

a) yohei.hamakawa@toshiba.co.jp

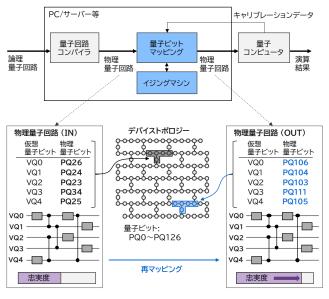

図1 システム構成および量子ビットマッピング

こと、高速・独立したプロセスであることからデバイスの最新のキャリブレーションデータを即時に反映可能である、のような特長が期待される. なお、アプローチは異なるが本手法と同様の目的を持つ従来手法が提案されており [34]、IBM 社が提供する量子ソフトウェア開発キットである Qiskit にも既に実装されている.

今回,はじめに従来手法との違いを定性的に評価するため,物理量子ビット数やトポロジーが異なる複数の仮想デバイスを用いてシミュレーションによる検証を行った.なお,イジングマシンには FPGA (Field Programmable Gate Array) に実装したシミュレーテッド分岐 (Simulated Bifurcation) [5,7] を採用した.この検証により,条件によってはマッピング精度と計算時間の双方で本提案手法に優位性があることがわかった.続けて,IBM 社の量子コンピュータ ibm\_kawasaki を対象とし,実際の物理的制約とキャリブレーションデータを使ってその優位性を評価した.

# 2. 提案手法

### 2.1 目的およびシステム構成

本提案手法を用いた量子コンピューティングシステム全体の構成を図1(上部)に示す.本稿では、ルーティングによる SWAP ゲート挿入やネイティブゲートへの変換および量子ビットマッピングが行われ、実行対象デバイスに対する物理的制約が解決された状態の量子回路(一般には量子回路コンパイラが出力するもの)のことを、物理量子回路と呼ぶことにする.本提案の量子ビットマッピングは、既に実行可能状態である物理量子回路に対し、デバイスのキャリブレーションデータを用いて、ノイズを考慮したより良い量子ビット割当(マッピング)を探索することを目的とする.また、この探索における組合せ最適化問題を、イジングマシンにより高速に求めることを特徴とする.

図 1 (下部) は、量子ビットマッピングの動作イメージを示す。ここでは、量子回路を構成する量子ビットの相対関係を識別するためにつけられた ID を仮想量子ビット (VQ0~VQ4)、デバイスの量子ビットを特定するためにつけられた ID を物理量子ビット (PQ0~PQ126)と呼ぶことにする。本提案の量子ビットマッピングでは、量子回路自体は変更せずに(仮想量子ビット間の相対関係を維持)、回路実行時の忠実度が最大になるようなマッピング(仮想量子ビットと物理量子ビットの対応関係)を決める。システム全体で見ると、既に量子回路コンパイラにより一度はマッピングが決まっているため、本提案手法は"再マッピング"を行う手法、とも言える。

### 2.2 イジング問題および QUBO

N 変数のイジング問題とは、次の式で定義されるイジングエネルギーを最小化するスピン構成を探索する問題である.

$$H_{\text{Ising}} = -\frac{1}{2} \sum_{i=1}^{N} \sum_{j=1}^{N} J_{i,j} s_i s_j + \sum_{i=1}^{N} h_i s_i,$$

(1)

ここで  $s_i$ ( $\in \{-1,1\}$ ) は i 番目のイジングスピン,  $J_{i,j}$  は i 番目と j 番目のスピン間の結合係数,  $h_i$  は i 番目のスピンのバイアス係数を表す.

QUBO とは、 $b_i \in \{0,1\}$  で表すバイナリ変数を目的変数とし、以下の式で定義されるコスト関数を最小にする問題である.

$$H_{\text{QUBO}} = \sum_{i}^{N} \sum_{j}^{N} Q_{i,j} b_i b_j, \qquad (2)$$

スピン変数  $s_i$  とバイナリ変数  $b_i$  は  $2b_i = s_i + 1$  の関係 にあり、イジング問題と QUBO は互いに線形変換することができる。イジングマシンは、イジング問題を解くのに特化した専用計算機であるが、線形変換により等価となる QUBO も解くことができる.

# 2.3 量子ビットマッピングの QUBO 定式化

本節では、量子ビットマッピングの QUBO 定式化手法 について説明する.

#### 2.3.1 QUBO 全体

ここでは、目的変数となるバイナリ変数  $x_{i,v}$  を以下のように定義する.

$$x_{i,v} = \begin{cases} 1, & (仮想量子ビット i を物理量子ビット v に割当), \\ 0, & (それ以外) \end{cases}$$

(3)

本提案の QUBO は、部分グラフ同型写像のための項  $(H_A, H_B, H_C)$  と忠実度最大化のための項  $(H_D, H_E)$  の線形結合として以下のように構成される.

$$H_{\text{remap}} = \alpha H_A + \beta H_B + \gamma H_C + \delta H_D + \epsilon H_E \qquad (4)$$

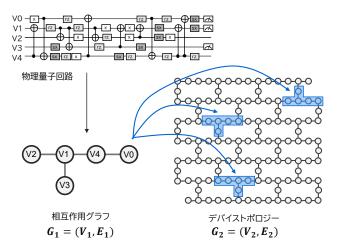

**図 2** 物理量子回路の相互作用グラフ $G_1$ からデバイストポロジー $G_2$ への部分グラフ同型写像

ここで  $\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\delta$ ,  $\epsilon$  は各項の重みを決める正の定数である. 次節より各項の詳細を説明する.

#### 2.3.2 部分グラフ同型写像(ペナルティ関数)

図 2 を参照しながら, "再コンパイル(再ルーティング) することなくマッピングが変更可能な条件"を QUBO の ペナルティ関数として表現する方法を説明する.

量子回路における量子ビット間接続関係は、相互作用グラフ(interaction graph)で表現することができる.相互作用グラフは、量子ビットによる頂点集合,CNOT ゲートなどの 2 量子ビットゲートによる接続関係を表したエッジ集合で構成される.ここでは、頂点集合を  $V_1$ 、辺集合を  $E_1$  として相互作用グラフを  $G_1=(V_1,E_1)$  と表記する.また,デバイスのトポロジーもグラフとして表現できる.ここでは,物理量子ビット集合を  $V_2$ 、物理量子ビット間接続を  $E_2$  とし,デバイストポロジーを  $G_2=(V_2,E_2)$  と表記する.このとき, $|V_1|\leq |V_2|$  かつ  $|E_1|\leq |E_2|$  である.以降,それぞれの頂点数を  $V_1=|V_1|$ 、 $V_2=|V_2|$  と表記する.

このとき,以下を満たす  $G_1$  から  $G_2$  への単射写像(部分グラフ同型写像)f が存在すれば,再ルーティングなしに量子ビットマッピングが可能であると言える.

$$\forall (i,j) \in E_1 \Rightarrow (f(i),f(j)) \in E_2 \tag{5}$$

この条件を QUBO で表現したものが以下の  $H_A$ ,  $H_B$ ,  $H_C$  である.

$$H_A = \sum_{i=1}^{N_1} \left( 1 - \sum_{v=1}^{N_2} x_{i,v} \right)^2 \tag{6}$$

$$H_B = \sum_{i \neq i'}^{N_1} \sum_{v=1}^{N_2} x_{i',v} x_{i,v} \tag{7}$$

$$H_C = \sum_{(i,j)\in E_1} \sum_{(u,v)\notin E_2} x_{i,u} x_{j,v}$$

(8)

$H_A$  は  $G_1$  の各頂点が  $G_2$  の任意の頂点に一つだけ対応するときに 0 をとり(いわゆる one-hot 制約), $H_B$  は  $G_2$  の

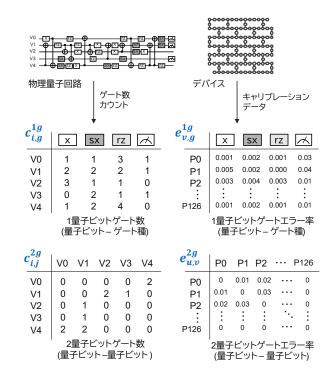

図 3 目的関数  $\log F_{\rm GM}$  の構成要素 (量子ビットゲート数,量子ビットゲートエラー率)

各頂点が  $G_1$  の任意の頂点に最大で 1 つ対応する場合に最小値 0 をとる.  $H_C$  は, $G_1$  に存在する辺が  $G_2$  に存在しない場合にペナルティが付加され,式 (5) を満たすときに最小値 0 をとる. つまり  $G_1$  が  $G_2$  に埋め込めるとき,ここで定義したペナルティ関数  $(H_A, H_B, H_C)$  は全て 0 となるよう設計される.

# 2.3.3 忠実度最大化(目的関数)

ここでは、マッピングの性能指標である"忠実度"を定義し、"忠実度最大化"を QUBO の目的関数として表現する方法を説明する.

量子回路中の量子ゲート集合 (measure も含む) を  $\{Q\}$ , 量子ゲート q がマッピング M により割当てられた量子ビット上で実行されるときのエラー率を  $\mathcal{E}[M[q]]$  と表記すると,マッピング後の回路全体の忠実度 (Fidelity, F), およびその相乗平均 (Geometric Mean of Fidelity,  $F_{GM}$ ) は,以下のように定義される.

$$F = \prod_{q \in \{Q\}} (1 - \mathcal{E}[\mathcal{M}[q]]) \tag{9}$$

$$F_{GM} = \left(\prod_{q \in \{Q\}} (1 - \mathcal{E}[\mathcal{M}[q]])\right)^{\frac{1}{|Q|}}$$

(10)

ここでは,任意の量子ゲート数を持つ量子回路に対して目的関数を設計するため  $F_{\rm GM}$  を最大化することを考える.ただし,マッピング M は  $x_{i,v}$  に相当するため,式 (10) の  $F_{\rm GM}$  は  $x_{i,v}$  の  $|\mathcal{Q}|$  次以上の項を持つことになり,QUBOでは表現できない.そこで今回は以下のように対数変換を行ったものを目的関数とする.

$$\log F_{\text{GM}} = \log \left( \left( \prod_{q \in \{Q\}} \left( 1 - \mathcal{E}[\mathcal{M}[q]] \right) \right)^{\frac{1}{|Q|}} \right)$$

(11)

$$= \frac{1}{|Q|} \sum_{q \in \{Q\}} \log \left( 1 - \mathcal{E}[\mathcal{M}[q]] \right)$$

(12)

図 3 に, $\log F_{\mathrm{GM}}$  の構成要素を示す. $c_{i,g}^{1g}$  は,物理量子 回路から 1 量子ビットゲートについて量子ビット (i) 毎, 量子ゲート種 (g) 毎にカウントされたゲート数を示す.  $c_{i,i}^{2g}$ は、物理量子回路中、量子ビット(i)、量子ビット(j)間に かかる2量子ビットゲートの数を示す. なお, 現在のデバ イスは基本的に2量子ビットゲートを1種類しか用意しな いため、ここではゲート種による分類は行っていない. ま た,デバイスによっては対称性を持たない (例えば CNOT ゲートや ECR ゲートにおいて、コントロールビットにな れる量子ビットとターゲットビットになれる量子ビットが 区別される) ため、方向性を考慮して  $c_{i,j}^{2g}$  を生成する. そ のため  $c_{i,j}^{2g} \neq c_{i,i}^{2g}$  となることもある.  $e_{v,g}^{1g}$  は、デバイスの キャリブレーションデータから1量子ビットゲートにつ いて物理量子ビット (v) 毎、量子ゲート種 (g) 毎に得たエ ラー率を示す. 同様に  $e_{u,v}^{2g}$  は, 物理量子ビット (u), 物理 量子ビット (v) にかかる 2 量子ビットゲートのエラー率を 示したものである.

以上の構成要素と  $x_{i,j}$  を用いて式 (12) を QUBO で表現したものが以下の  $H_D$ ,  $H_E$  である.

$$H_D = -\frac{1}{|\mathcal{Q}|} \sum_{g \in \{I\}} \sum_{i,v}^{N_1, N_2} c_{i,g}^{1g} \log(1 - e_{v,g}^{1g}) x_{i,v}$$

(13)

$$H_E = -\frac{1}{|\mathcal{Q}|} \sum_{\substack{(i,j) \in E_1 \\ (u,v) \in E_2}} c_{i,j}^{2g} \log(1 - e_{u,v}^{2g}) x_{i,u} x_{j,v}$$

(14)

ここで  $\{I\}$  はデバイスが持つ量子ゲート種の集合を意味する. また、QUBO では目的関数の最小化を行うため、 $\log F_{\rm GM}$  の最大化を目的とする本項については符号を反転している.

#### **3. 評価実験**

#### 3.1 従来手法 (MAPOMATIC)

提案手法の評価にあたり、従来手法である MAPO-MATIC [34] を比較対象とする。MAPOMATIC も、量子回路コンパイラの後段に位置し、キャリブレーションデータを用いて忠実度の高いマッピングを再探索する最適化アルゴリズムである。再ルーティングすることなくマッピングを行うために、量子回路の相互作用グラフ  $G_1$  とデバイスのトポロジー  $G_2$  に対し部分グラフ同型問題を解く。この部分グラフの抽出アルゴリズムとして、厳密解法である VF2++ [35] を採用していることが本提案との大きな違いである。MAPOMATIC では、VF2++ により全てのマッピング候補を列挙した後、式 (9) により全候補の忠実度を

計算し、最も忠実度が高いマッピングを選択する. なお、部分グラフ同型問題は NP 完全問題であり、最悪の場合の計算量は指数的に増加する. そのため、MAPOMATIC では部分グラフの探索において呼び出し制限 (call limit, 試行回数の上限を指定)を設けている.

なお、MAPOMATIC は OSS として単体でも提供されているが、VF2PostLayout モジュールとして Qiskit のトランスパイラ(量子回路コンパイラ)にも組み込まれている.

# 3.2 イジングマシン(シミュレーテッド分岐)

シミュレーテッド分岐 (Simulated Bifurcation, SB) [5,7] は,量子分岐マシンと呼ばれる量子断熱最適化手法 [36] に対する古典対応物から導かれた,量子に着想を得た最適化計算アルゴリズムである.分岐現象を示す古典的な非線形振動子ネットワークの断熱時間発展を数値的に模擬すること,つまり,古典計算機による力学系のシミュレーションに基づくアルゴリズムであることが特徴的な点である.SBには adiabatic SB (aSB),ballistic SB (bSB),discrete SB (dSB) などのいくつかのバリエーションがあるが,本研究では以下の式で定義される bSB をイジングマシンとして採用した.

$$y_i^{t_{k+1}} \leftarrow y_i^{t_k} + \left[ -(a_0 - a^{t_k}) x_i^{t_k} - \eta h_i + c_0 \sum_{j=1}^{N} J_{i,j} x_j^{t_k} \right] \Delta_t,$$

(15)

$$x_i^{t_{k+1}} \leftarrow x_i^{t_k} + a_0 y_i^{t_{k+1}} \Delta_t, \tag{16}$$

$$(x_i^{t_{k+1}}, y_i^{t_{k+1}}) \leftarrow \begin{cases} (\operatorname{sgn}(x_i^{t_{k+1}}), 0) & (\text{if } |x_i^{t_{k+1}}| > 1), \\ (x_i^{t_{k+1}}, y_i^{t_{k+1}}) & (\text{if } |x_i^{t_{k+1}}| \le 1), \end{cases}$$

(17)

ここで、 $x_i$  と  $y_i$  は、それぞれ i 番目の振動子(i 番目の振動子は i 番目のスピンに対応)の位置と運動量を表す実数であり、 $a_0$ ,  $c_0$ ,  $\eta$  は正の定数,a(t) は 0 から  $a_0$  まで増加する制御パラメータである. 1 イテレーションあたりの時間増加分を  $\Delta_t$  と表記したとき, $t_{k+1}=t_k+\Delta_t$  となる. この更新プロセスを  $N_{\text{step}}$  回繰り返した後, $x_i$  を 2 値化 (±1) し,i 番目のスピンとしイジング問題の解として用いる.

#### 3.3 初期評価:多様な条件下での比較

# 3.3.1 評価方法

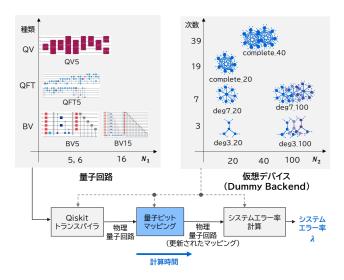

図 4 に、初期評価における評価系を示す。まずは本提案手法の定性的な特徴を把握するため、従来手法とともに多様な条件下で量子マッピングを行い、その性能を測定した。入力となる量子回路には、Bernstein-Vazirani (BV)、Quantum Fourier Transform (QFT)、Quantum Volume (QV)の3種類、量子ビット数に5、6、16のバリエーションを用意した。また、デバイスには物理量子ビット数と1頂点あたりの次数(頂点に接続している辺の数)の異なる

図 4 初期評価における評価系

6 つのバリエーション( $\deg D_-N_2$ : 次数 D で量子ビット数が  $N_2$  のグラフ,complete\_ $N_2$ : 量子ビット数  $N_2$  の完全グラフ,前者は  $D\in\{3,7\}$ , $N_2\in\{20,100\}$ ,後者は  $N_2\in\{20,40\}$ ) のトポロジーを持つ仮想デバイスを Qisikit の (Dammy)Backend モジュールとして用意した.

これらを組合せた全ての条件において、用意した量子回路を Qiskit でトランスパイルし、得られた物理量子回路を入力として量子ビットマッピング(本提案手法または従来手法(MAPOMATIC))を行う.

量子ビットマッピングの性能指標としては、以下で定義されるシステムエラー率  $(\lambda)$  と、量子ビットマッピングに要した計算時間を用いた.

$$\lambda = 1 - F = 1 - \prod_{q \in \{\mathcal{Q}\}} \left( 1 - \mathcal{E}[\mathcal{M}[q]] \right) \tag{18}$$

# 3.3.2 実験環境

本実験は、下記の計算機環境で実施した.

- OS: CentOS Linux 7.8

- CPU: Intel Core i5-9400 CPU @ 2.90GHz (6-Core)

- BAM: 8 GB

- FPGA: Intel FPGA PAC D5005 (Intel 10 SX GX2800 FPGA)

量子回路コンパイラには Qiskit (version 1.1.1) を用い、最適化レベル (optimization\_level) は規定値の 1 を使用した.比較対象である MAPOMATIC は、スタンドアロン版の version  $0.13.0^{*1}$ を用い、全てのパラメータについて規定値を使用した.

bSB アルゴリズムを 2,048 スピン全結合, 32 ビット浮動小数点精度の仕様で上記 FPGA に実装したものをイジングマシンとして使用した([37] と同じものであり、システムクロック周波数は 259MHz)。なお、式 (15) におい

https://github.com/qiskit-community/MAPOMATIC

図 5 初期評価結果:棒グラフが  $\lambda \downarrow$  (システムエラー率),折れ線グラフが計算時間  $(s) \downarrow$  を表す.仮想トポロジー毎にグラフを分け,各グラフ内で量子回路毎また手法毎に  $\lambda$  と計算時間をプロット.

て、 $a_0=1$ 、 $c=c_0=\eta$  とし、今回は提案手法の適用可能性を探るためにc、 $\Delta_t$  および  $N_{\rm step}$  の値を問題毎に探索した(以降の評価結果(計算時間)において、このパラメータ探索のための時間は含まない).

#### 3.3.3 評価結果

初期評価結果を図 5 に示す.まず従来手法との差において最も顕著なのが,量子回路に BV5 または BV15 を選んだ場合である.ここでは全てのトポロジーにおいて,MAPOMATIC に対し本提案手法の計算時間が圧倒的に小さいことがわかる.さらに,BV15 では  $\deg_3$ 20 を除く全てのトポロジーにおいて  $\lambda$  も小さくなることがわかる.これは,MAPOMATIC が採用する VF2++が最適解を求める厳密解法であるにも関わらず,本ケースにおいては実用時間内に全てのマッピング候補を列挙できず,MAPOMATICで最適解が得られなかったことが要因である.

次に、計算時間のデバイストポロジーに対する依存性を見てみる。次数3と次数7のトポロジー間ではそれほど大きな依存性は見られなかったが、完全グラフ(complete\_20、complete\_40)では、提案手法とMAPOMATICで大きな差が見られる。ここでは全ての量子回路入力についてMAPOMATICの計算時間が数百秒から数千秒と膨大となることに対し、本提案手法では2秒以内と極めて高速であることが確認できる。

<sup>\*1</sup> MAPOMATIC:

#### 情報処理学会研究報告

IPSJ SIG Technical Report

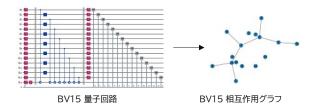

図 6 BV15 (Bernstein-Vazirani) の量子回路と相互作用グラフ

$\lambda$  に関しては、QFT5 および QV5 と deg7\_100 の組合せにおいて提案手法が僅かに劣るものの、その他多くのケースでは同等であり、かつ前記の通り MAPOMATIC が実用時間内に最適解を求められないケースにおいて提案手法が優位となることもあった。

#### 3.3.4 結果の分析

本節では、初期評価において特に計算時間と $\lambda$ において差が大きかった Bernstein-Vazirani 回路(BV5,BV15)について考察する。 図 6 は,BV15 の量子回路実装例と,この量子回路を deg3\_20 向けに量子回路コンパイルされた物理量子回路から得られる相互作用グラフを示したものである。ここでは相互作用グラフが非連結グラフになっていることが特徴として挙げられる。これは,Bernstein-Vaziraniの量子回路実装において,オラクル関数部も含め,必ずしも全ての量子ビットが他のいずれかの量子ビットと相互作用を行わないからである。図 6 の相互作用グラフは,このような量子ビットが,孤立頂点として複数存在する様子を表している。

非連結グラフでは、各連結成分を独立して考慮する必要があるため、探索すべき部分グラフの候補が大幅に増加する. そのため、VF2++のような厳密解法においては、計算時間が爆発的に増加したと推定される. 一方、提案手法のようにこれをイジング問題として解く場合には、グラフの連結・非連結によって計算量は変化しないため、他の問題を扱うのと同様に安定的かつ高速に解くことができた、と考えられる.

# 3.4 追加評価: 非連結グラフと実データによる検証3.4.1 問題設定

最後に、本提案手法の優位性を実在の量子コンピュータ のデバイストポロジーと実用的なタスクの組合せにて検証 する.

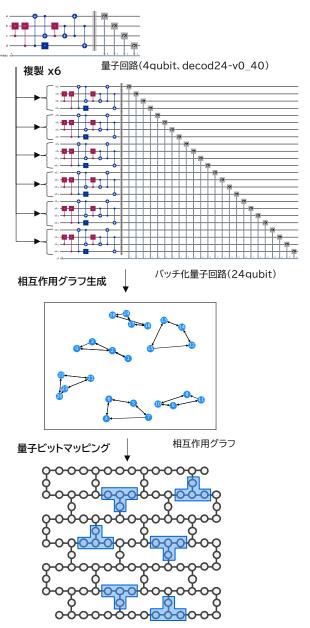

本提案手法に大きな優位性が見られた"相互作用グラフが非連結となる条件"に相当する実用的なタスクの例として、今回は"バッチ並列実行"(図7)を選ぶ.複数の小規模(量子ビット数が小さい)回路を、1つの大規模(物理量子ビット数が大きい)デバイスに割当てることで、1回のデバイス実行において複数の問題を同時に解くような実行方法を、本稿ではバッチ並列実行と呼ぶ.図7は、4量子ビットの回路(ここでは、Revlib [38] からワンホットデ

デバイストポロジー (ibm\_kawasaki)

図 7 バッチ並列実行イメージ:4 量子ビットの小規模回路を6つ複製した24 量子ビットの回路を生成(バッチ化量子回路). 相互作用グラフは非連結となる.

コード回路である "decod24-v0\_40" を採用)を 6 つ複製して統合した 24 量子ビットの量子回路によりバッチ並列実行を行う例を示している. もちろん, バッチ化される前の小規模回路間には相互作用がないため相互作用グラフは非連結となる.

実在の量子コンピュータデバイスとして、IBM Q の ibm\_kawasaki インスタンスを選んだ。ibm\_kawasaki は 127 量子ビットの Eagle r3 プロセッサを搭載した量子 コンピュータ\*2であり、デバイストポロジーは heavy hex lattice 構造をとる。なお、ibm\_kawasaki がサポートする 2

<sup>\*2 2021</sup> 年の稼働開始時点では 27 量子ビットの Falcon プロセッサ を搭載していたが、2023 年にリプレースされた.

#### 情報処理学会研究報告

IPSJ SIG Technical Report

表 1 評価結果: ibm\_kawasaki 上でのバッチ並列実行

| Method    | $\lambda\downarrow$ | 計算時間(s)↓ |

|-----------|---------------------|----------|

| MAPOMATIC | 0.95                | 4463     |

| 提案手法      | 0.77                | 51       |

量子ビットゲート(ECR ゲート)には方向性があるため, $G_1$ (相互作用グラフ)および  $G_2$ (デバイストポロジー)はそれぞれ有向グラフとなる.

#### 3.4.2 実験環境

本実験は、FPGA 実装イジングマシンのスピン数 2,048 を超える QUBO を扱うため、3.3.2 とは異なる以下の環境にて実施した.

- OS: Ubuntu 22.04

- CPU: Intel Xeon Silver 4215R CPU @ 3.20GHz (16-Core)

- RAM: 384 GB

- GPU: NVIDIA GeForce RTX 4060 Ti (16GB)

bSB アルゴリズムを CUDA 12.4 を用いて上記 GPU で動作するソフトウェアとして実装し、これをイジングマシンとして使用した.その他のソフトウェア条件については3.3.2 と同様である.

### 3.4.3 評価結果

評価結果を**表 1** に示す。 $\lambda$ ,計算時間の双方において,提案手法が従来手法である MAPOMATIC を大きく上回る性能を発揮していることが確認できた.

# 4. まとめ

ゲート型量子コンピュータの量子ビットマッピングにおいて、再ルーティング不要かつノイズを考慮したマッピング最適化手法を提案した。本提案手法は、部分グラフ同型問題と忠実度最大化問題を一つのQUBOに定式化しイジングマシンでこれを解くことで、コンパイル済みの量子回路を変更することなく、デバイストポロジー制約の範囲内で信頼度の高いマッピングを高速に探索することが特長である。仮想トポロジーを用いた多様な条件下での検証、またibm.kawasakiのトポロジーとキャリブレーションデータを用いた検証において、完全グラフのような高密度なトポロジーにおいて計算時間に優位性があること、また、トポロジーに依らず量子回路の相互作用グラフが非連結となる場合に計算時間および忠実度指標において優れた性能を発揮することが確認できた。

現時点では、問題毎に最良解を得るためのイジングマシンのパラメータが異なり、それを人手で調整する必要があるなど実用性の観点で課題がある。今後、パラメータ自動調整の仕組みを導入するなどの課題解決や改良を行いながら、例えば量子 OS におけるバッチ割当、タスクスケジューラ、ディスパッチャなど、本提案手法特有の長所が活きる応用先の開拓および実用性の検証を進めたい。

# 参考文献

- Gushu Li, Yufei Ding, and Yuan Xie. Tackling the qubit mapping problem for nisq-era quantum devices. CoRR, abs/1809.02573, 2018.

- [2] Alexander Cowtan, Silas Dilkes, Ross Duncan, Alexandre Krajenbrink, Will Simmons, and Seyon Sivarajah. On the qubit routing problem. 2019.

- [3] Prakash Murali, Jonathan M. Baker, Ali Javadi Abhari, Frederic T. Chong, and Margaret Martonosi. Noiseadaptive compiler mappings for noisy intermediate-scale quantum computers, 2019.

- Giovanni Finocchio, Jean Anne C Incorvia, Joseph S Friedman, Qu Yang, Anna Giordano, Julie Grollier, Hyunsoo Yang, Florin Ciubotaru, Andrii V Chumak, Azad J Naeemi, Sorin D Cotofana, Riccardo Tomasello, Christos Panagopoulos, Mario Carpentieri, Peng Lin, Gang Pan, J Joshua Yang, Aida Todri-Sanial, Gabriele Boschetto, Kremena Makasheva, Vinod K Sangwan, Amit Ranjan Trivedi, Mark C Hersam, Kerem Y Camsari, Peter L McMahon, Supriyo Datta, Belita Koiller, Gabriel H Aguilar, Guilherme P Temporao, Davi R Rodrigues, Satoshi Sunada, Karin Everschor-Sitte, Kosuke Tatsumura, Hayato Goto, Vito Puliafito, Johan Akerman, Hiroki Takesue, Massimiliano Di Ventra, Yuriy V Pershin, Saibal Mukhopadhyay, Kaushik Roy, I-Ting Wang, Wang Kang, Yao Zhu, Brajesh Kumar Kaushik, Jennifer Hasler, Samiran Ganguly, Avik W Ghosh, William Levy, Vwani Roychowdhury, and Supriyo Bandyopadhyay. Roadmap for unconventional computing with nanotechnology. Nano Futures, 8(1):012001, mar 2024.

- [5] Hayato Goto, Kosuke Tatsumura, and Alexander R. Dixon. Combinatorial optimization by simulating adiabatic bifurcations in nonlinear hamiltonian systems. Science Advances, 5(4):eaav2372, 2019.

- [6] Kosuke Tatsumura, Alexander R. Dixon, and Hayato Goto. FPGA-based simulated bifurcation machine. In 2019 29th International Conference on Field Programmable Logic and Applications (FPL), pages 59–66, 2019

- [7] Hayato Goto, Kotaro Endo, Masaru Suzuki, Yoshisato Sakai, Taro Kanao, Yohei Hamakawa, Ryo Hidaka, Masaya Yamasaki, and Kosuke Tatsumura. Highperformance combinatorial optimization based on classical mechanics. Science Advances, 7(6):eabe7953, 2021.

- [8] Kosuke Tatsumura, Masaya Yamasaki, and Hayato Goto. Scaling out ising machines using a multi-chip architecture for simulated bifurcation. *Nature Electronics*, 4(3):208–217, Mar 2021.

- [9] Taro Kanao and Hayato Goto. Simulated bifurcation for higher-order cost functions. Applied Physics Express, 16(1):014501, dec 2022.

- [10] Tomoya Kashimata, Masaya Yamasaki, Ryo Hidaka, and Kosuke Tatsumura. Efficient and scalable architecture for multiple-chip implementation of simulated bifurcation machines. *IEEE Access*, 12:36606–36621, 2024.

- [11] M. W. Johnson, M. H. S. Amin, S. Gildert, T. Lanting, F. Hamze, N. Dickson, R. Harris, A. J. Berkley, J. Johansson, P. Bunyk, E. M. Chapple, C. Enderud, J. P. Hilton, K. Karimi, E. Ladizinsky, N. Ladizinsky, T. Oh, I. Perminov, C. Rich, M. C. Thom, E. Tolkacheva, C. J. S. Truncik, S. Uchaikin, J. Wang, B. Wilson, and G. Rose. Quantum annealing with manufactured spins. Nature, 473(7346):194–198, May 2011.

- [12] Andrew D. King, Jack Raymond, Trevor Lanting,

- Richard Harris, Alex Zucca, Fabio Altomare, Andrew J. Berkley, Kelly Boothby, Sara Ejtemaee, Colin Enderud, Emile Hoskinson, Shuiyuan Huang, Eric Ladizinsky, Allison J. R. MacDonald, Gaelen Marsden, Reza Molavi, Travis Oh, Gabriel Poulin-Lamarre, Mauricio Reis, Chris Rich, Yuki Sato, Nicholas Tsai, Mark Volkmann, Jed D. Whittaker, Jason Yao, Anders W. Sandvik, and Mohammad H. Amin. Quantum critical dynamics in a 5,000-qubit programmable spin glass. *Nature*, 617(7959):61–66, May 2023.

- [13] Toshimori Honjo, Tomohiro Sonobe, Kensuke Inaba, Takahiro Inagaki, Takuya Ikuta, Yasuhiro Yamada, Takushi Kazama, Koji Enbutsu, Takeshi Umeki, Ryoichi Kasahara, Ken ichi Kawarabayashi, and Hiroki Takesue. 100,000-spin coherent ising machine. Science Advances, 7(40):eabh0952, 2021.

- [14] Kirill P. Kalinin, Alberto Amo, Jacqueline Bloch, and Natalia G. Berloff. Polaritonic xy-ising machine. *Nanophotonics*, 9(13):4127–4138, 2020.

- [15] Fabian Böhm, Guy Verschaffelt, and Guy Van der Sande. A poor man's coherent ising machine based on opto-electronic feedback systems for solving optimization problems. *Nature Communications*, 10(1):3538, Aug 2019.

- [16] Fuxi Cai, Suhas Kumar, Thomas Van Vaerenbergh, Xia Sheng, Rui Liu, Can Li, Zhan Liu, Martin Foltin, Shimeng Yu, Qiangfei Xia, J. Joshua Yang, Raymond Beausoleil, Wei D. Lu, and John Paul Strachan. Power-efficient combinatorial optimization using intrinsic noise in memristor hopfield neural networks. Nature Electronics, 3(7):409–418, Jul 2020.

- [17] William A. Borders, Ahmed Z. Pervaiz, Shunsuke Fukami, Kerem Y. Camsari, Hideo Ohno, and Supriyo Datta. Integer factorization using stochastic magnetic tunnel junctions. *Nature*, 573(7774):390–393, Sep 2019.

- [18] Navid Anjum Aadit, Andrea Grimaldi, Mario Carpentieri, Luke Theogarajan, John M. Martinis, Giovanni Finocchio, and Kerem Y. Camsari. Massively parallel probabilistic computing with sparse ising machines. *Nature Electronics*, 5(7):460–468, Jul 2022.

- [19] Artem Litvinenko, Roman Khymyn, Victor H. Gonzalez, Roman Ovcharov, Ahmad A. Awad, Vasyl Tyberkevych, Andrei Slavin, and Johan Akerman. A spinwave ising machine. *Communications Physics*, 6(1):227, Aug 2023.

- [20] Markus Graber and Klaus Hofmann. An integrated coupled oscillator network to solve optimization problems. Communications Engineering, 3(1):116, Aug 2024.

- [21] William Moy, Ibrahim Ahmed, Po-wei Chiu, John Moy, Sachin S. Sapatnekar, and Chris H. Kim. A 1,968-node coupled ring oscillator circuit for combinatorial optimization problem solving. *Nature Electronics*, 5(5):310–317, May 2022.

- [22] Dagur Ingi Albertsson, Mohammad Zahedinejad, Afshin Houshang, Roman Khymyn, Johan Akerman, and Ana Rusu. Ultrafast ising machines using spin torque nanooscillators. Applied Physics Letters, 118(11):112404, 03 2021.

- [23] Tianshi Wang, Leon Wu, Parth Nobel, and Jaijeet Roychowdhury. Solving combinatorial optimisation problems using oscillator based ising machines. *Natural Comput*ing, 20(2):287–306, Jun 2021.

- [24] Anshujit Sharma, Richard Afoakwa, Zeljko Ignjatovic, and Michael Huang. Increasing ising machine capacity with multi-chip architectures. In Proceedings of the 49th Annual International Symposium on Computer Architecture, ISCA '22, page 508?521, New York, NY, USA,

- 2022. Association for Computing Machinery.

- [25] Kazushi Kawamura, Jaehoon Yu, Daiki Okonogi, Satoru Jimbo, Genta Inoue, Akira Hyodo, Angel Lopez Garcia-Arias, Kota Ando, Bruno Hideki Fukushima-Kimura, Ryota Yasudo, Thiem Van Chu, and Masato Motomura. Amorphica: 4-replica 512 fully connected spin 336mhz metamorphic annealer with programmable optimization strategy and compressed-spin-transfer multi-chip extension. In 2023 IEEE International Solid-State Circuits Conference (ISSCC), pages 42–44, 2023.

- [26] Satoshi Matsubara, Motomu Takatsu, Toshiyuki Miyazawa, Takayuki Shibasaki, Yasuhiro Watanabe, Kazuya Takemoto, and Hirotaka Tamura. Digital annealer for high-speed solving of combinatorial optimization problems and its applications. In 2020 25th Asia and South Pacific Design Automation Conference (ASP-DAC), pages 667–672, 2020.

- [27] Hasitha Muthumala Waidyasooriya and Masanori Hariyama. Highly-parallel FPGA accelerator for simulated quantum annealing. IEEE Transactions on Emerging Topics in Computing, 9(4):2019–2029, 2021.

- [28] Takuya Okuyama, Tomohiro Sonobe, Ken-ichi Kawarabayashi, and Masanao Yamaoka. Binary optimization by momentum annealing. *Phys. Rev. E*, 100:012111, Jul 2019.

- [29] Timothee Leleu, Farad Khoyratee, Timothee Levi, Ryan Hamerly, Takashi Kohno, and Kazuyuki Aihara. Scaling advantage of chaotic amplitude control for highperformance combinatorial optimization. *Communica*tions Physics, 4(1):266, Dec 2021.

- [30] Andrew Lucas. Ising formulations of many np problems. Frontiers in Physics, 2, 2014.

- [31] Soshun Naito, Yoshihiko Hasegawa, Yoshiki Matsuda, and Shu Tanaka. Isaaq: Ising machine assisted quantum compiler, 2023.

- [32] Bryan Dury and Olivia Di Matteo. A qubo formulation for qubit allocation, 2020.

- [33] Anastasiia Butko, Ilyas Turimbetov, George Michelogiannakis, David Donofrio, Didem Unat, and John Shalf. Tiger: Topology-aware assignment using ising machines application to classical algorithm tasks and quantum circuit gates, 2020.

- [34] Paul D. Nation and Matthew Treinish. Suppressing quantum circuit errors due to system variability. PRX Quantum, 4:010327, Mar 2023.

- [35] Alpár Jüttner and Péter Madarasi. VF2++—An improved subgraph isomorphism algorithm. *Discrete Applied Mathematics*, 242:69–81, 2018. Computational Advances in Combinatorial Optimization.

- [36] Hayato Goto. Bifurcation-based adiabatic quantum computation with a nonlinear oscillator network. Scientific Reports, 6(1):21686, Feb 2016.

- [37] Ryo Hidaka, Yohei Hamakawa, Jun Nakayama, and Kosuke Tatsumura. Correlation-diversified portfolio construction by finding maximum independent set in largescale market graph. *IEEE Access*, 11:142979–142991, 2023.

- [38] Robert Wille, Daniel Grose, Lisa Teuber, Gerhard W. Dueck, and Rolf Drechsler. Revlib: An online resource for reversible functions and reversible circuits. In 38th International Symposium on Multiple Valued Logic (ismul 2008), pages 220–225, 2008.